# DIGITAL MEETS ANALOG

# CHAPTER 13

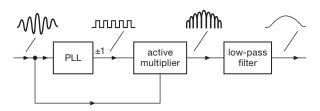

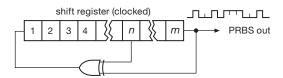

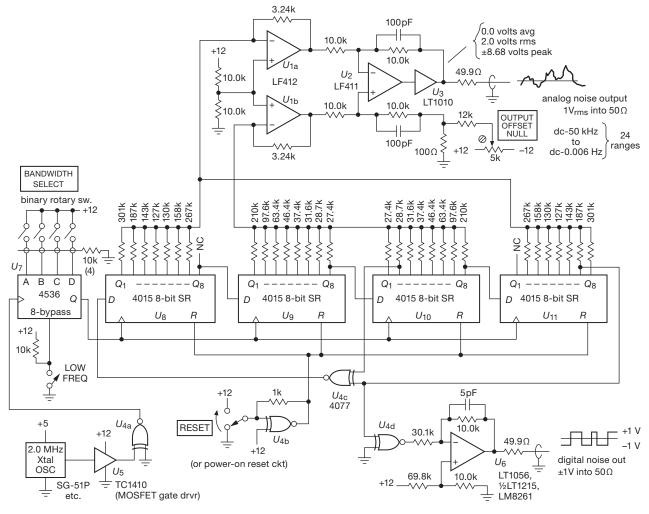

Here we meet the major subject of conversion between analog and digital signals – analog-to-digital (A/D) and digital-to-analog (D/A) converters (ADCs and DACs) – as well as the important "mixed-signal" phase-locked loop (PLL). And we cannot resist a look at the fascinating topic of pseudorandom noise generation.

We live in a largely analog (continuous) world - of sounds, images, distances, times, voltages and currents, and so on - which would seem to call for analog circuits (oscillators, amplifiers, filters, combiners, etc.). But we live also in a partly digital (discrete) world - of numbers and arithmetic, of text and symbols, and the like - which would seem to call for digital circuits (arithmetic logic and storage, etc.). And that's how it was, for many years: analog amplifiers and filters for audio and video; analog oscillators, tuned circuits, and mixers for radio and television; and even *analog computers*, for solving differential equations<sup>1</sup> or for real-time control of flight or weaponry. Meanwhile digital techniques (initially with mechanisms and relays, then with vacuum tubes, followed by discrete transistors, small-scale ICs, and finally the large and fast microprocessors with a billion+ transistors that we take for granted) were used for computational tasks like keeping track of money, and of words.

But the almost miraculous improvements in the speeds and densities of purely digital electronics have produced a major paradigm shift, namely, the use of digital conditioning and processing for nearly every "analog" quantity. For example, audio engineers now digitize the individual microphone signals at the time of recording, and perform all subsequent mixing and conditioning (e.g., the addition of reverberation) as arithmetic on those numbers; the same goes for digital video. And at the everyday level, digital techniques have invaded our lives: the authors' bathroom scales indicate to 0.1 pound (sometimes to our regret) – that's a resolution<sup>2</sup> of a part per thousand; our porch light is switched on and off by a digital wall switch that follows the seasonal variation of dusk and dawn; and our automobiles depend on a digital bus, to which are connected some 50 or more embedded digital controllers for functions like engine control and diagnostics, braking, air bags, entertainment, climate control, and so on.

The bottom line is that A/D and D/A conversion techniques have become central to every aspect of analog measurement and control. This is important stuff, and it is the major subject of this chapter. Let's go at it.

Our treatment of the various conversion techniques is not aimed at developing skill in converter design itself. Rather, we try to point out the advantages and disadvantages of each method, because in most cases the sensible thing is to buy commercially available chips or modules, rather than to build the converter from scratch. An understanding of conversion techniques and idiosyncrasies will guide you in choosing from among the thousands of available units.

# 13.1 Some preliminaries

# 13.1.1 The basic performance parameters

Before getting into lots of detail, we'd like to summarize the important performance parameters that you need to keep in mind when choosing ADCs and DACs. Knowing what you need makes it a lot easier to find what you want.

# Digital-to-analog converters

| <b>Resolution:</b> number of bits                                          |

|----------------------------------------------------------------------------|

| Accuracy: monotonicity; linearity; dc stability                            |

| Reference: internal or external; multiplying DAC                           |

| (MDAC)?                                                                    |

| Output type: voltage output or current output                              |

| <b>Output scaling:</b> unipolarity or bipolarity; V <sub>out</sub> ranges; |

| <i>I</i> <sub>out</sub> compliance                                         |

| <b>Speed:</b> settling time; update rate                                   |

Although the bathroom scale reads with a *resolution* of 0.1 pound, its accuracy is likely poorer (perhaps to  $\pm 1$  pound), with some drift over time and temperature.

<sup>&</sup>lt;sup>1</sup> There's a nice example of this in the section on Analog Function Circuits in Chapter *4x*: modeling the fascinating chaotic behavior of the system of nonlinear differential equations devised by Lorenz.

$<sup>^2</sup>$  To be distinguished from *accuracy* – recall the discussion in §5.1.1.

**Quantity:** single or multiple DACs/pkg

- **Digital input format:** serial (I<sup>2</sup>C, SPI, or a variant) or parallel

- Package: module, through-hole, or various surfacemount packages

- **Other:** glitch energy; power-on state; programmable internal digital scaling

# Analog-to-digital converters

Resolution: number of bits

Accuracy: monotonicity; linearity; dc stability

**Reference:** internal or external

**Input scaling:** unipolarity or bipolarity; voltage range **Speed:** conversion time and latency

**Quantity:** single or multiple ADCs/pkg

- **Digital-output format:** serial (I<sup>2</sup>C, SPI, or a variant) or parallel

- **Package:** module, through-hole, or various surfacemount packages

- **Other:** internal programmable gain amplifier (PGA); spur-free dynamic range (SFDR)

# 13.1.2 Codes

At this point you should review §10.1.3 on the various number codes used to represent signed numbers. Offset binary and 2s complement are commonly used in A/D conversion schemes, with sign-magnitude and Gray codes also popping up from time to time. Here is a reminder:

|               | Offset       | 2s           |

|---------------|--------------|--------------|

|               | binary       | Complement   |

| +Full scale   | 11111111     | 01111111     |

| +Full scale-1 | 11111110     | 01111110     |

| $\downarrow$  | $\downarrow$ | $\downarrow$ |

| 0+1 LSB       | 10000001     | 00000001     |

| 0             | 1000000      | 00000000     |

| 0-1 LSB       | 01111111     | 11111111     |

| $\downarrow$  | $\downarrow$ | $\downarrow$ |

| -Full scale+1 | 00000001     | 1000001      |

| -Full scale   | 00000000     | 1000000      |

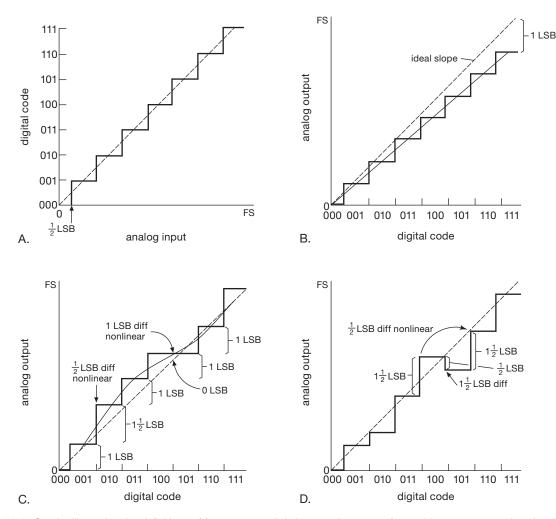

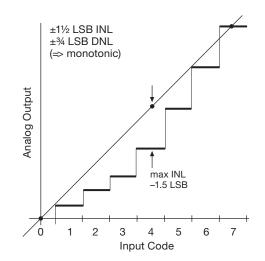

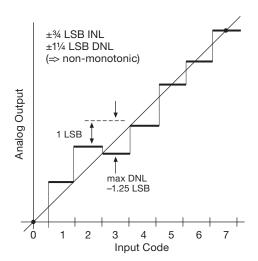

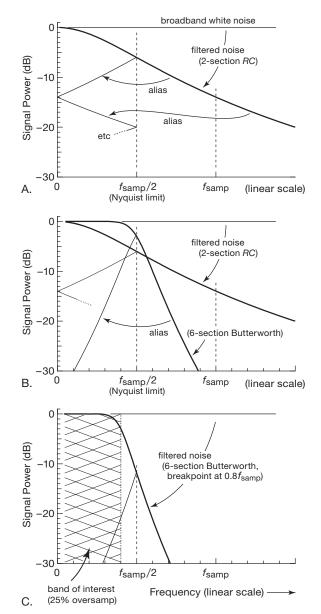

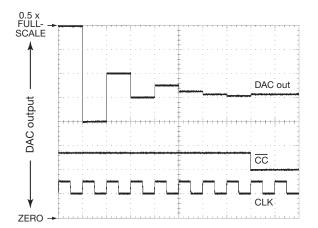

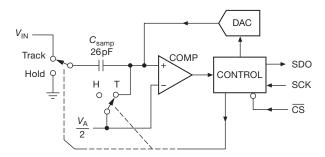

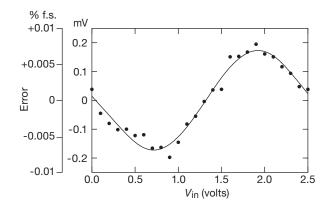

# 13.1.3 Converter errors

The subject of ADC and DAC errors is a complicated one, about which whole volumes could be written. According to Bernie Gordon at Analogic, if you think a highaccuracy converter system lives up to its claimed specifications, you probably haven't looked closely enough. We won't go into the application scenarios necessary to support Bernie's claim, but it's worth a first look at the four most common types of converter errors: offset error, scale error, nonlinearity, and nonmonotonicity, nicely illustrated in the self-explanatory Figure 13.1. Rather than boring you with a long-winded discussion, though, we'll move directly to a description of D/A converter techniques and capabilities. Then we'll revisit the business of converter errors (§13.4), which will make a lot more sense in context.

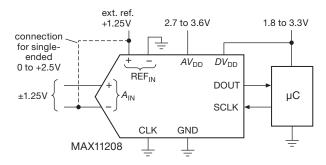

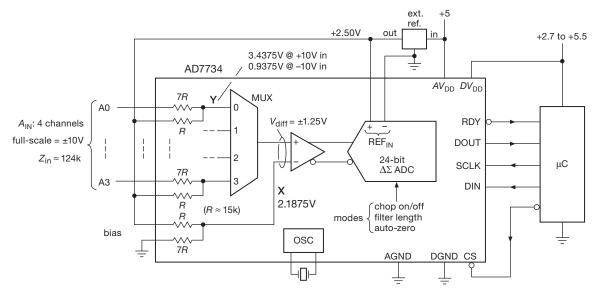

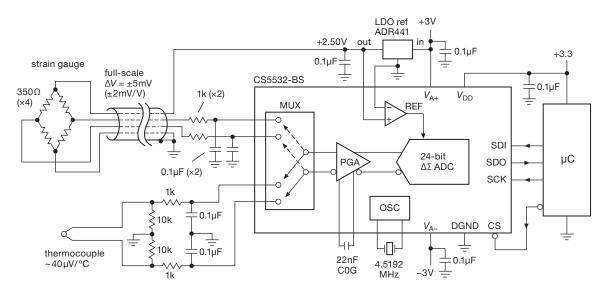

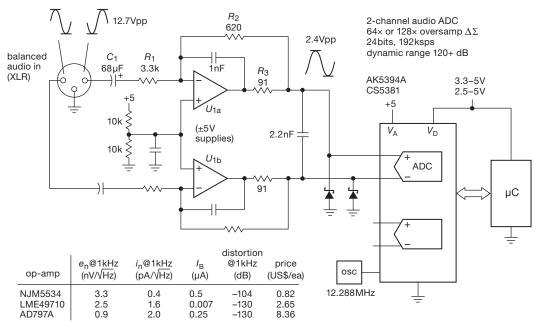

#### 13.1.4 Stand-alone versus integrated

Sometimes an ADC or DAC (or both) is integrated into a fancier IC. The most common example is the microcontroller (Chapter 15), where you frequently see both ADCs and DACs integrated on the same chip as the processor and its other I/O peripherals. As far as we can tell, the least-expensive stand-alone ADC costs significantly more than the least-expensive microcontroller-with-ADC.<sup>3</sup> Microcontrollers are fond of integrating lots of useful peripherals, along with program and data memory, so that you've got essentially a "system-on-a-chip." Be aware, though, that these converters that come bundled with inexpensive general-purpose microcontrollers do not attain the excellent performance of a good stand-alone converter: you can get 8-bit or even 10-bit performance; but you won't get 16 bits, and nothing approaching the 24-bit performance of a high-quality audio ADC.<sup>4</sup>

For some classes of IC, though, an integrated converter delivers excellent performance. One example is a direct digital synthesis (DDS) chip (§7.1.8), where on-chip phase counters and a sine lookup table create digital values of the synthesized sinewave output; these things can clock at speeds of 1 GHz or more, with an on-chip 14-bit (for example) DAC generating the analog output signal. Another example comes from the video world, where it's common to see digital video processing and conversion functions combined on a single high-performance IC. And in the audio business you see parts like the Cirrus CS470xx-series (their "All-In-One Audio IC" system-on-a-chip), which includes multiple 24-bit ADCs and DACs with 105 dB dynamic range, integrated onto a chip that has a 32-bit DSP (with 32 kB RAM), audio codecs and sample rate

<sup>&</sup>lt;sup>3</sup> To wit: National's ADC0831 8-bit ADC costs \$1.85, whereas Microchip's PIC10F with its 8-bit ADC and 2-input multiplexer costs \$0.48 (both in quantity 25).

<sup>&</sup>lt;sup>4</sup> A shining exception is provided by Analog Devices' series of "Analog Microcontrollers," with honest performance to 16 or 24 bits. You might think of these as consisting of a high-quality converter core, with a quiet microcontroller tacked on.

**Figure 13.1.** Graphs illustrating the definitions of four common digital conversion errors, for a 3-bit converter over its 8 levels from 0 to full scale (FS). A. ADC transfer curve,  $\frac{1}{2}$ LSB offset at zero. B. Linear, 1 LSB scale error. C.  $\pm \frac{1}{2}$ LSB nonlinearity (implies 1 LSB possible error); 1 LSB differential nonlinearity (implies monotonicity). D. Nonmonotonic (must be  $> \pm \frac{1}{2}$ LSB nonlinear). Used with permission of Texas Instruments Inc.

converters, digital audio ports (SPDIF), and an SPI/I<sup>2</sup>C control port.

Stand-alone converters are dominant, though, in highaccuracy and high-linearity applications (voltmeters; quality audio gear). They also provide a tremendous selection range, in terms of the many parameters just listed, as compared with the rather limited selection of on-chip converters you find in microcontrollers.

# 13.2 Digital-to-analog converters

The goal is to convert a quantity specified as a binary (or multidigit BCD, see §10.1.3B) number to a voltage, or to a current, proportional to the value of the digital input.

There are several popular methods: (a) resistor string with MOS switches; (b) R-2R ladder; (c) binary-scaled current sources; and (d) delta–sigma (and other pulse-averaging) converters. Let's take them in turns.

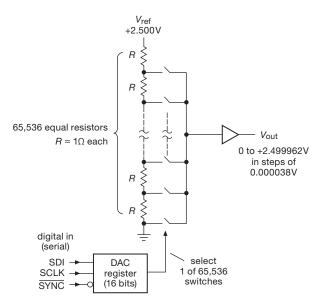

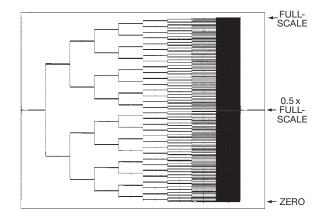

# 13.2.1 Resistor-string DACs

This method is about as straightforward as you can get. A string of  $2^n$  equal-value resistors is connected between a stable voltage reference and ground, creating a very tall voltage divider; and a set of MOSFET analog switches is used to route the selected tap's voltage to an output voltage buffer (Figure 13.2). The figure shows the configuration of TI's impressive DAC8564, a quad 16-bit DAC (four

independent DACs in one package), each section having a string of  $2^{16}$  (65,536) resistors connected between a precision internal +2.5 V reference and ground. Quoting from the terse description in the datasheet, "The code loaded into the DAC register determines at which node on the string the voltage is tapped off to be fed into the output amplifier by closing one of the switches connecting the string to the amplifier."<sup>5</sup>

**Figure 13.2.** An easy-to-understand DAC: the digital input selects the corresponding MOSFET switch tap on a giant voltage divider. TI crams four of these into their DAC8564.

This method has the virtue of guaranteed monotonicity. As the datasheet puts it (even more tersely than before), "It is monotonic because it is a string of resistors." And this particular DAC exhibits other nice qualities, specifically low *glitch energy* (spikes that appear at the output during code transitions), excellent accuracy and stability (worst-case values of  $\pm 0.02\%$  initial accuracy and 5 ppm/°C tempco), rail-to-rail output ("RRO") with a single positive supply (+2.7–5.5 V), and low power (1 mA, typ). This puppy costs about \$12. The same method is used in DACs of more modest performance, for example National's DAC121: 12-bit, voltage output, micropower (150  $\mu$ A) single-supply with rail-to-rail input and output (RRIO). The latter is a single DAC without internal reference (full scale is the positive supply), and of course it has "only" 4096 resistors in

its string; it costs under \$2. Both of these (and most other converters these days) use a serial digital input, which for these particular converters is the simple 3-wire SPI (see \$14.7). See also the discussion of digital potentiometers in \$3.4.3E.

# 13.2.2 R-2R ladder DACs

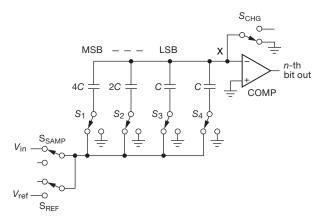

A string of  $2^{16}$  matched resistors and switches is a pretty impressive piece of engineering. But the exponential number of components eventually overwhelms engineering finesse. An attractive alternative is the *R*–2*R* ladder, which collapses the requirement to an array of just 2*n* matched resistors (versus  $2^n$ ) for an *n*-bit DAC.

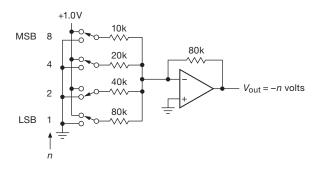

**Figure 13.3.** Summing scaled currents to create a simple DAC. Simple to understand, but never used in practice: an R-2R network is used instead.

To get started, consider the simple notional scheme shown in Figure 13.3: the resistor values are in a binary sequence, so their binary-weighted currents at the summing junction produce a binary-weighted voltage output. Simple, but not terribly practical with more than a few bits, because the resistor values must span a wide range, and with increasingly demanding accuracy for the lower resistance values; of greater worry still is the need for very low switch  $R_{on}$  corresponding to the low resistance values.<sup>6</sup>

**Exercise 13.1.** Design a 2-digit BCD DAC. Assume that the inputs are 0 or +1 volt; the output should go from 0 to 9.9 volts.

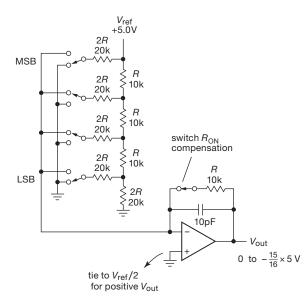

Instead, the scheme shown in Figure 13.4 is used. It's easy to convince yourself that this clever arrangement produces a binary-weighted current into the op-amp's summing junction, therefore a corresponding output voltage. And only two resistor values are needed (R and 2R, which, however, must both be accurately replicated and in a precise 2:1 ratio), regardless of the number of bits.

<sup>&</sup>lt;sup>5</sup> These guys seem not to be fond of commas. We were tempted to add a few, to pace the breathless flow of the sentence. But, hey, a quote is a quote, right?

<sup>&</sup>lt;sup>6</sup> This method does have the flexibility, however, of allowing arbitrary bit weights.

**Figure 13.4.** An R-2R ladder network generates a binary-scaled output current into the op-amp's summing junction, producing a voltage-output DAC.

There are many excellent R-2R DACs out there. For example, TI's DAC9881 is an 18-bit voltage-output DAC with an SPI serial input; it is guaranteed monotonic,<sup>7</sup> with integral linearity to  $\pm 2$  LSB. It requires an external voltage reference ( $V_{ref}$ ), which sets the full-scale voltage (the noninverting input is biased at  $V_{ref}/2$ , for positive output polarity). It excels in accuracy and low noise, and costs about \$30.

**Exercise 13.2.** Prove that the foregoing *R*-2*R* ladder works as advertised.

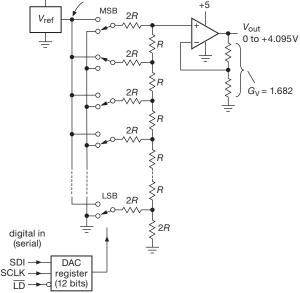

In practice, most R–2R DACs use the alternative configuration of Figure 13.5, in which the output of the R–2R network is itself a voltage. For example, the TI DAC7611 is a 12-bit voltage-output DAC (+4.095 V full-scale output, popular for DACs that run from +5 V) with an SPI serial input and on-chip voltage reference; it's linear and monotonic to its full 12 bits, comes in an 8-pin package, and costs about \$4.

**Figure 13.5.** *R*–2*R* voltage-output DAC, in the more common voltage-combining configuration.

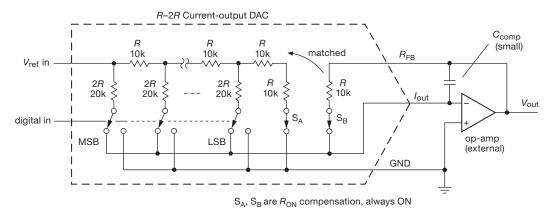

Figure 13.6. Classic current-switched DAC.

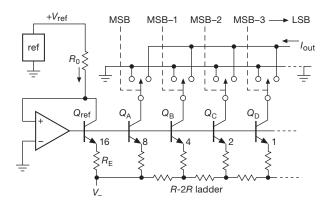

# 13.2.3 Current-steering DACs

The preceding converters generate *voltage* outputs. This is often most convenient, but the op-amp tends to be the slowest part of the converter circuit. In situations where you can use a converter with *current* output, you'll get better speeds, and usually at lower price. Some additional advantages of current-output DACs are: (a) flexible choice of current-to-voltage op-amp, for example to minimize noise, or to produce a larger output voltage swing; (b) the ability to combine several DAC outputs directly; and (c) the availability of *multiplying DACs* (see next subsection), in which

<sup>&</sup>lt;sup>7</sup> Note that, unlike a resistor-string DAC, an *R*–2*R* DAC is not *guaranteed* monotonic when resistor tolerances are taken into account. The semiconductor industry does a good job, however, and most *R*–2*R* DACs are monotonic to 1 LSB.

0 - FFFF

the output current is the product of the digital input code and an analog signal applied to the  $V_{ref}$  input.

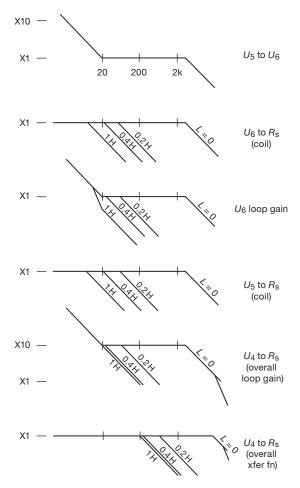

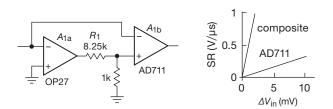

better capability in the 0 dB to -40 dB region out to 10 MHz.

Figure 13.6 shows how these "current-steering" converters work. The currents can be generated by an array of transistor current sources with scaled emitter resistors, although IC designers usually use instead an R-2R ladder of emitter resistors. In most converters of this type, the current sources are ON all the time, and their output current is switched to the output terminal or to ground, under control of the digital input code. Watch out for limited output compliance in current-output DACs; it can be as little as 0.5 V, though values of a few volts are typical.

Some examples of current-steering DACs (with serial digital inputs and internal voltage references) are the LTC1668 (16 bits, 20 ns settling time into a 50  $\Omega$  load as "voltage out," output compliance to  $\pm 1$  V, about \$20) and

the TI DAC5682 (dual, 16 bits, 10 ns settling time, output compliance to  $V_+\pm0.5$  V, about \$45). For *real* speed, there's the AD9739 (14 bits, 2500 Msps!). On a more modest scale there's the industry-standard DAC/LTC8043 (external voltage reference input, 12 bits, 0.25  $\mu$ s settling time into 100  $\Omega$ , about \$6), and the similar parallel-input AD/LTC7541.

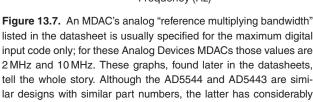

#### 13.2.4 Multiplying DACs

Note that these latter two converters require an external voltage reference, an apparent disadvantage that can be turned into an advantage: they accept a continuous range of V<sub>ref</sub> input voltages, of either polarity. In other words, the (current) output is proportional to the product of the digital input and the analog reference voltage: it's a "multiplying DAC" (MDAC). Furthermore, the product can be positive or negative; so its full name is a "four-quadrant multiplying DAC." Examples of higher-resolution four-quadrant MDACs are the 16-bit DAC8814 (serial input) and closely similar DAC8820 (parallel input). Multiplying DACs specify both their conversion precision (linearity, monotonicity) and the bandwidth of the analog multiplying input (i.e.,  $V_{\rm ref}$ ); for these two converters the "reference multiplying bandwidths" are 10 MHz and 8 MHz, respectively, with respective prices of \$25 and \$15.

Note that not all DACs are optimized for use in this way, so it is best to check the datasheets of the converters you're considering for details. A DAC with good multiplying properties (wide analog input range, high speed, etc.) will usually be called a "multiplying DAC" right at the top of the datasheet. Table 13.3 on page 894 lists selected Multiplying DACs.

*A caution*: the specified bandwidth can be seriously misleading, owing to the effects of capacitive feedthrough. Figure 13.7 shows this behavior, as illustrated in the respective datasheets of these two MDACs.

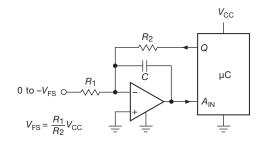

Multiplying DACs (and the ADC equivalent) open the possibility of *ratiometric* measurements and conversions. If a sensor of some sort (e.g., a variable-resistance transducer like a thermistor) is energized by the same voltage that also supplies the reference for the ADC, then variations in the reference voltage will not affect the measurement. This concept is very powerful, because it permits measurement and control with accuracy greater than the stability of voltage references or power supplies; conversely, it relaxes the requirements on supply stability and accuracy. The ratiometric principle is used in its simplest form in the classic *bridge* circuit, in which two ratios are adjusted to equality by nulling the differential signal taken

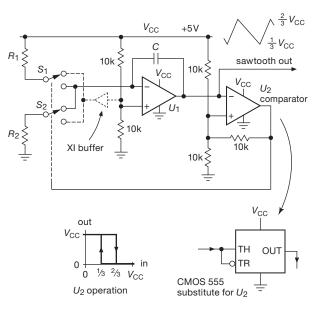

Figure 13.8. Generating voltages from current-output DACs.

between the two voltage-divider outputs. Devices like the 555 (see §7.1.3) achieve good stability of output frequency with large variations of supply voltage by using essentially a ratiometric scheme: the capacitor voltage, generated by an *RC* network from the supply, is compared with a fixed fraction of the supply voltage  $(\frac{1}{3}V_{CC} \text{ and } \frac{2}{3}V_{CC})$ , giving an output frequency that depends only on the *RC* time constant.<sup>8</sup> We will have more to say on this important subject in connection with ADCs later in this chapter.

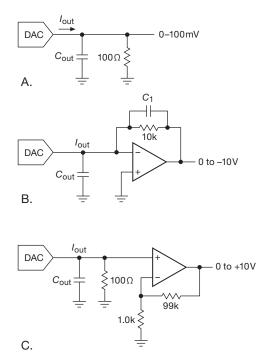

# 13.2.5 Generating a voltage output

If you've chosen a voltage-output DAC, you're done! But with a current-output DAC you've got to use one of several schemes for generating a voltage output. Figure 13.8 shows some ideas. If the load capacitance is low and large voltage swings aren't needed, a simple resistor to ground will do nicely (but see warning, below). This is what's usually done with video DACs. For example, the THS8133 triple 10-bit video DAC generates full-scale output currents of 26.7 mA, which produce a standard 1.0 V analog video signal when driving doubly terminated 75  $\Omega$  coax. This method works fine also for general applications: with the usual 1 mA full-scale output current, a 50  $\Omega$  load resistor will give 50 mV full-scale output with 50  $\Omega$  output impedance. If the capacitance of the DAC's output combined with the load capacitance doesn't exceed 100 pF, you will get 50 ns settling time in the preceding example, assuming the DAC is that fast. When worrying about the effect of *RC* time constants on DAC output response, don't forget that it takes quite a few *RC* time constants for the output to settle to within  $\frac{1}{2}$  LSB of the final voltage. It takes 7.6 *RC* time constants, for instance, to settle to within 1 part in 2048, which is what you would want for a 10-bit converter output.

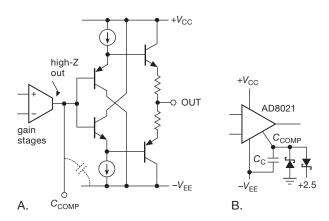

To generate large swings, or to buffer into small load resistances or large load capacitances, an op-amp can be used in the transresistance configuration (current-to-voltage amplifier), as shown. The capacitor across the feedback resistor may be necessary for stability, because the DAC's output capacitance in combination with the feedback resistance introduces a lagging phase shift; unfortunately, that compromises the speed of the amplifier. It is an irony of this circuit that a relatively expensive high-speed (fast-settling) op-amp may be necessary to maintain the high speed of even an inexpensive DAC.<sup>9</sup> In practice, the last circuit may give better high-speed performance, since no compensation capacitor is needed. Watch out for offset voltage error, because the op-amp's input offset voltage is amplified by the voltage gain (here a factor of 100).

An Important Warning: when using current-output DACs, note that both the initial accuracy (e.g., full-scale  $I_{out}$ ) and the stability of the current output may be grotesquely poor, relative to the DACs resolution. It is not uncommon to see a spread of as much as 2:1 (!) in the full-scale current. What to do? Most current-output DACs include a built-in feedback resistor, closely matched to the R-2R resistors, intended to be used with an external op-amp (Figure 13.9). If you don't use it, you may have gain errors of  $\pm 25\%$  or more; and even if you trim away this gain error, there will be residual gain *drift* (not usually specified on datasheets) that typically will be 100 times larger than you get with the internal resistor.

To give an example, the LTC8043 is an improved version of the industry-standard DAC8043 12-bit multiplying

<sup>&</sup>lt;sup>8</sup> We showed analogous ratiometric schemes in §§4.3.5, 4.6.4, 7.1.3D, and 10.4.5A.

<sup>&</sup>lt;sup>9</sup> Some current-output DACs have surprisingly-high output capacitance,  $C_{out}$ , e.g., as much as 200 pF for the LTC7541 12-bit MDAC. So you need a stabilizing capacitor  $C_1$ , of value  $C_1 > \sqrt{C_{out}/2\pi f_T R_f}$ , as discussed before, see for example §§8.11.6 and 4x.3. Choose an op-amp, then, with a high enough  $f_T$  so that  $C_1$  is small enough for the desired speed. Some fast current-output DACs take pains to keep  $C_{out}$  small, as little as 5 pF.

**Figure 13.9.** Current-output R-2R DAC with internal feedback resistor matched to the precision network resistors both in initial resistance and in temperature coefficient. Ignore  $R_{FB}$  at your peril!

DAC. In the best grade (-E suffix) it specifies a gain error of  $\pm 1\%$  (max), and a gain tempco of 5 ppm/°C (max). (It also guarantees maximum integral and differential nonlinearities of  $\pm 0.5\%$ ; see the discussion in §13.4.) Impressive specs. Note, however, that the gain specifications state "Using internal feedback resistor." What if you don't? The datasheet doesn't say! But you can tease the answer from what it *does* say, namely that the input resistance of the R-2*R* network (seen at the  $V_{ref}$  input) is 11 k $\Omega$  (nominal), with limits of  $7 k\Omega$  (min) and  $15 k\Omega$  (max). That is, this DAC, which guarantees an admirable gain accuracy of  $\pm 0.024\%$ when the matched internal feedback resistor is used in conjunction with an external op-amp, would deliver a shockingly poor<sup>10</sup>  $\pm 35\%$  absolute gain error as a current-output device (or, equivalently, with an external feedback resistor and op-amp, for voltage output).<sup>11</sup>

Bottom line: if a current-output DAC gives you an internal feedback resistor, you need to think long and hard before deciding not to use it.

Another bottom line: if you want a bipolarity outputvoltage range, you might be tempted to sink a reference current (derived from  $V_{ref}$ ) from the summing junction in Figure 13.9. *Don't do it!* Instead, append a difference amplifier to  $V_{out}$ , using an offset of  $V_{ref}/2$  for the other input.

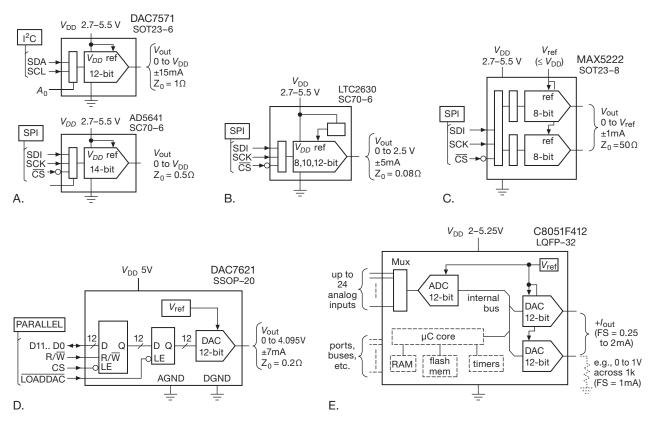

# 13.2.6 Six DACs

To give a further sense of what's out there, let's look at a few examples of relatively simple DACs of modest performance. By "modest" we mean that these converters do not push close to the limits of speed or accuracy; rather, they're inexpensive, compact, and easy to use. You can drop them onto a circuit board, and off you go. Later, in §13.3, we'll look at some applications that demand DACs of greater performance; in those situations you'll need carefully designed surrounding circuitry to exploit fully the advanced capabilities of the converter.

Take a look at Figure 13.10, with reference to Table 13.1. These were chosen somewhat arbitrarily from the many thousands (no kidding!) of available DACs, though we did make an effort to select devices from multiple manufacturers. They range from 8 to 14 bits, with settling times of  $4-10 \,\mu$ s. Except for E, they are all voltage-output devices.

Taking it from the top of Figure 13.10: A–C are singlesupply low-voltage parts with serial interfaces, so they can fit into tiny SOT23 or (even tinier) SC70 packages. The pair in A use the supply voltage as reference, with the fullscale output voltage  $V_{\rm FS}$  equal to the supply  $V_{\rm DD}$ ; one uses an SPI interface (with the usual chip select), whereas the other uses an I<sup>2</sup>C interface (with the input pin  $A_0$  selecting between factory preset bus addresses of decimal 76 or 77).<sup>12</sup> If you want a fixed and stable reference voltage, rather than using  $V_{\rm DD}$ , a converter like the LTC2630 in B is a good choice. Its internal reference has adequate

<sup>&</sup>lt;sup>10</sup> I'm shocked, shocked to find that gain inaccuracy and drift is going on in here!

<sup>&</sup>lt;sup>11</sup> You might ask why an IC manufacturer whose chips deliver outstanding accuracy has a problem making resistors with even "pretty good" absolute accuracy. Good question. Turns out that the process is optimized for best *tracking*, with overall resistor scaling only of secondary importance.

<sup>&</sup>lt;sup>12</sup> The DAC7512 from the same manufacturer substitutes SPI for I<sup>2</sup>C; and the AD5601/11/21 are less-expensive 8- to 12-bit versions of the 14-bit AD5641.

**Figure 13.10.** Six DACs, whose specifications are listed in Table 13.1. The DAC7571, LTC2630, and MAX5222 in the upper row are typical of inexpensive serial-input converters in small packages (see §14.7 for discussion of the SPI and I<sup>2</sup>C serial interfaces). The DAC7621 uses a traditional parallel data input; and the C8051 is a general-purpose microcontroller that includes a pair of current-output DACs among its many internal assets.

stability for a converter of this precision ( $\pm 10 \text{ ppm}/^{\circ}\text{C}$ , typ), though its absolute accuracy is only modest (full-scale error of  $\pm 0.2\%$  typ,  $\pm 0.8\%$  worst case). The LTC2630 family includes a "high-voltage" variant with a 4.096 V internal reference (thus 1.0 mV/LSB), for which the  $V_{\text{DD}}$  range is narrowed to 4.5–5.5 V (5 V nominal); it also includes 8- and 10-bit variants.

Although you *could* imagine squeezing two converters into a 6-pin package (e.g., with an  $I^2C$  2-wire interface and no choice of address), the converter in C takes the rational choice of adding two pins, which both accommodates the SPI port (three wires, including Cs') and allows an external reference.<sup>13</sup> By reducing the lead pitch (from 0.95 mm to 0.65 mm) this 8-pin device fits in the same overall package size ( $1.6 \times 2.9$  mm) as the 6-pin SOT23-6. The bottom row illustrates a converter with a parallel input port, an interface that has largely gone out of popularity except for converters that operate at the highest speeds (e.g., the 2500 Msps AD9739 in §13.2.3). But there are applications for which this is useful, even at modest speeds, for example if you want to use the *n*-bit output of a counter directly: no microcontroller, no programming... just wires.

Finally, the last "converter" E is actually just some carry-on baggage belonging to a full-function microcontroller, complete with on-chip program memory (flash ROM), SRAM, timers, ports (parallel, SPI, UART), accurate oscillator, and even a 24-channel (multiplexed) 12-bit 200 ksps ADC. The dual DACs use an internal reference, and produce a current-sourcing output (with programmable full-scale ranges of 0.25–2 mA, by factors of 2) with compliance to 1.2 V below the supply rail (which runs over a wide range of 2.0–5.25 V). Oh, and did we mention that this thing includes a computational core that runs at

<sup>&</sup>lt;sup>13</sup> One small fly in the ointment here is the lack of double buffering along with an 8-bit data payload; thus the two channels cannot be updated to different values simultaneously.

50 million instructions per second? Or that it includes onchip full-speed in-system debugging? Or that you can get it also in a diminutive 5 mm square QFN-28 package? Quite a performance!

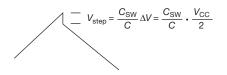

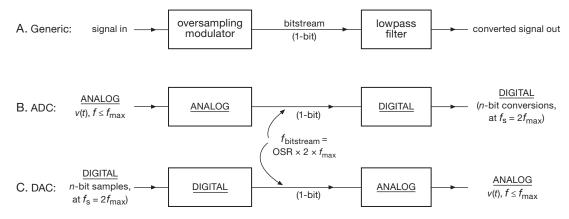

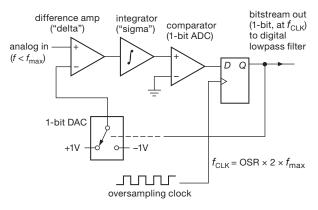

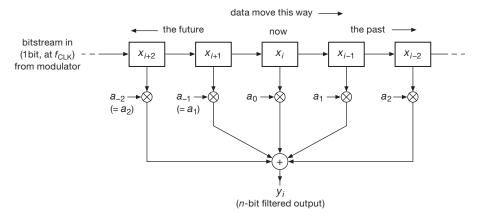

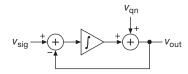

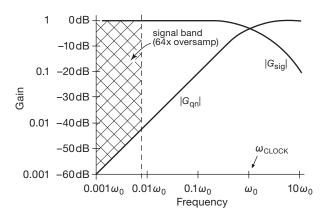

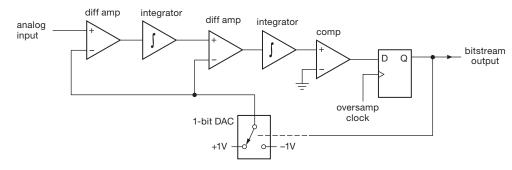

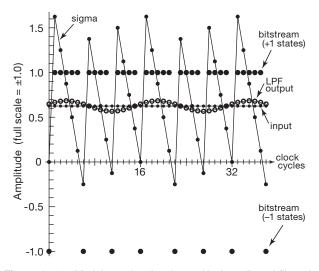

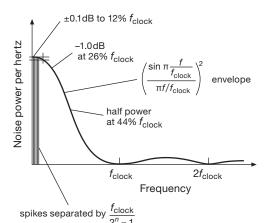

# 13.2.7 Delta-sigma DACs

The final DAC technique is somewhat weird, and not so easily understood in all its richness. (See Table 13.11 on page 939.) We'll describe it in detail later in the chapter (§13.9). Very roughly speaking, the technique consists of generating a train of fixed-amplitude pulses, at a high clock rate, on a single output line. These pulses are all of the same width, and are either present or absent at each clocking interval, according to the digital input code. (You could imagine simply generating a regular train of pulses, with a duty cycle proportional to the input code; but the delta– sigma process is considerably more sophisticated, as explained in §13.9.) This pulse train is then lowpass filtered, with a cutoff well below the clock frequency, to generate the analog output.

This is sometimes called a "1-bit DAC." That's a seriously misleading name, though, because these things in fact deliver stunningly linear output signals of high resolution. They are widely used in professional audio. A nice example is the ADI AD1955 dual (stereo) ADC, which delivers 20-bit analog audio output (120 dB dynamic range) when clocked at 12 MHz.<sup>14</sup>

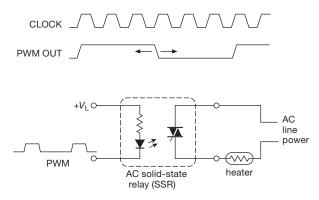

#### 13.2.8 PWM as digital-to-analog converter

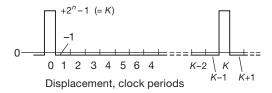

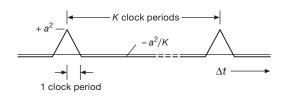

One last method of driving an analog system from a digital quantity is via *pulse-width modulation* (PWM). This is qualitatively different from the true DACs just described, because it does not generate an analog output directly; but it is widely used for power loads such as a heater. The idea is to run a repeating cycle of N clock cycles, during which the load is switched ON for some smaller number of clock cycles k, and OFF for the rest, with the fraction (duty cycle) k/N proportional to the digital input (Figure 13.11). This is easily done with a counter, magnitude comparator, and high-frequency clock (see Exercise 13.3). The slowly responding load does the averaging over the full cycle. This is more efficient than driving the load with a properly smoothed analog signal, because the driver is a switch, with very little dissipation; a switch is also simpler than a linear amplifier. This technique is popular in "class-D" audio power amplifiers (§2.4.1C) and in other power-control applications such as stepping motors and dc servomotors (§9.9). Many microcontrollers are configured with internal PWM timer modes; even lacking that, you can always program it in software.

**Figure 13.11.** Pulse-width modulator (PWM) as time-averaged DAC, for slow power loads. For an ac-powered load (as shown) the clock should be synchronous with the powerline.

Although a simple lowpass filter could be used to generate an output voltage proportional to the average time spent in the HIGH state (i.e., proportional to the digital input code), pulse-width modulators are most often used when the load is itself a slowly responding system. The pulsewidth modulator then generates precise parcels of energy, averaged by the system connected as a load. For example, the load might be capacitive (as in a switching regulator, see Chapter 9), thermal (a thermostated bath with heater), mechanical (a tape-speed servo, variable-speed motor, or stepping motor), or electromagnetic (a large electromagnet controller).

PWM outputs are attractive both for their simplicity and for their natural match to digital devices like counters and power-driving switches (MOSFETs); but there are some serious tradeoffs. For example, to get high PWM resolution for the k/N fraction, we need a large N. But the timer has a maximum clock rate  $f_{clk}$ , which sets a lower cycle rate  $f_c = f_{clk}/N$ . For a PWM that is within a feedback loop (as in the PWM discussion in §15.6) this implies reduced loop bandwidth and gain.

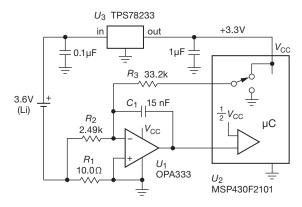

In practice you'll most likely encounter digital PWM hardware in a microcontroller. Sometimes you can choose a specific  $\mu$ C on account of its PWM capabilities, but more often not. For example, further along in §13.9.11B we choose TI's MSP430F2101 because it has an analog comparator. So, what kind of PWM does one get in the MSP430x2xx family? This information is not in the

<sup>&</sup>lt;sup>14</sup> It does cheat, however, by generating several parallel 1-bit streams internally; it's a "multibit" delta–sigma ADC. More on this, and other delta–sigma amusements, in §13.9.

| Table 13  | .1 Si           | хC       | Digi   | tal-to-                     | Anal              | log C              | onve                         | erters                         |                  |                             |                    |                                 |       |      |                       |

|-----------|-----------------|----------|--------|-----------------------------|-------------------|--------------------|------------------------------|--------------------------------|------------------|-----------------------------|--------------------|---------------------------------|-------|------|-----------------------|

| _         | Bits            | Channels | Output | t <sub>settle</sub><br>(µs) | Tot<br>min<br>(V) | al V<br>max<br>(V) | <b>Ι<sub>S</sub></b><br>(μΑ) | bus/Mbps                       | Refei<br>type    | rence<br>error <sup>m</sup> | Out<br>Zout<br>(Ω) | put<br>/ <sub>out</sub><br>(mA) | pkg   | pins | Cost<br>qty 1<br>\$US |

| DAC7571   | 12              | 1        | V      | 10                          | 2.7               | 5.5                | 140                          | l <sup>2</sup> C / 4.8         | $V_{\rm DD}$     | 0.2%                        | 1                  | ±15                             | SOT23 | 6    | 4.65                  |

| AD5641    | 14              | 1        | V      | 6                           | 2.7               | 5.5                | 75                           | SPI / 30                       | $V_{\rm DD}$     | 0.04%                       | 0.5                | ±5                              | SC70  | 6    | 5.40                  |

| LTC2630   | 12 <sup>a</sup> | 1        | V      | 4.4                         | 2.7               | 5.5                | 180                          | SPI / 50                       | 2.5 <sup>c</sup> | 0.8%                        | 0.08               | ±15                             | SC70  | 6    | 3.70                  |

| MAX5222   | 8               | 2        | V      | 10                          | 2.7               | 5.5                | 380                          | SPI / 25                       | ext              | 10mV                        | 50                 | ±1                              | SOT23 | 8    | 3.00                  |

| DAC7621   | 12              | 1        | V      | 7                           | 4.7               | 5.3                | 500                          | parallel <sup>d</sup>          | 4.096            | 0.4%                        | 0.2                | ±7                              | SSOP  | 20   | 7.00                  |

| C8051F412 | 12              | 2        | Ι      | 10                          | 2                 | 5.3                | l <sub>out</sub>             | µC internal                    | 2mA <sup>e</sup> | 2%                          | CS                 | NA                              | LQFP  | 32   | 7.80                  |

|           |                 |          |        |                             |                   |                    |                              | ic OK. (c) cho<br>2mA, by fact |                  |                             |                    |                                 |       |      | max.                  |

52- or 88-page datasheets; we had to consult the 693-page "MSP430x2xx Family Users Guide," where 40 pages were devoted to Timers A and B.

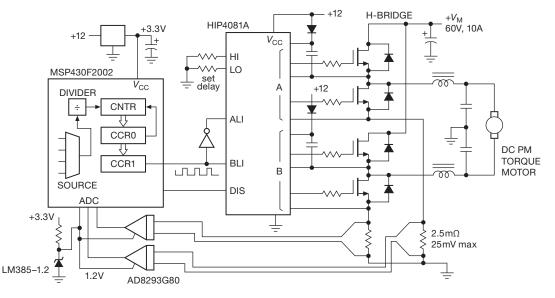

Figure 13.12 shows the MSP430F2002 member of this microcontroller family (which has a 10-bit ADC instead of a comparator) driving a dc torque motor. We've arranged four MOSFETs with an H-bridge driver and the controller's PWM signal to set the current. Naively, you'd expect that a 50% duty cycle would correspond to zero motor current; but that's true only when the motor is stopped, because the motor's "back EMF" disturbs this simple concept. Here we've used two sense resistors to measure the forward or reverse currents, with a pair of G=80 instrumentation amplifiers (§5.15) to inform the  $\mu$ C's ADC so it can servo the PWM to set the desired motor current and torque.<sup>15</sup> The amplifiers can operate from a single supply if their output reference pin is at least +0.8 V (see Table 5.8 on page 363); here we used a 1.25 V zener-type IC reference.

The microcontroller has a pair of 16-bit timers with programmable input selectors and dividers. They can run as fast as 16 MHz, which results in a cycle frequency of  $f_c=244$  Hz if we use the full 16-bit resolution. You can program the length N to less than  $2^{16}$ , but remember that the timer's other users have to live with your choice. Timer A has two capture/compare registers (CCR1 and CCR2), which can be used in compare mode to generate two PWM outputs (CCR0 is already used to set N). For example, let's say we need a speedier cycle rate of  $f_c=10$  kHz, and we stick with the maximum 16 MHz clock. We set the counter's modulus  $N=f_{clk}/f_c=1600$  counts, and our PWM

resolution will be limited to... about 10 bits. My goodness, only 10 bits?<sup>16</sup>

This example illustrates that a favorable alternative to PWM may involve attaching a few external DACs to a microcontroller. Another possibility is to drive the MOS-FET switch with the internal bitstream (if provided on an external pin) of a delta–sigma DAC, with its improved resolution–bandwidth tradeoff (compared with  $f_c = f_{clk}/N$  for the simple PWM).<sup>17</sup>

**Exercise 13.3.** Design a circuit to generate a 10 kHz train of pulses of width proportional to an 8-bit binary input code. Use counters and magnitude comparators (suitably expanded).

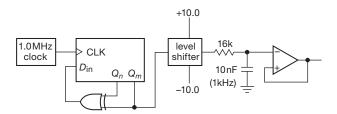

# A. An unusual PWM DAC

We close the PWM discussion by mentioning an unusual DAC from Linear Technology. Their LTC2644 (dual) and 2645 (quad) are PWM-to-DAC converters (a DAC with a digital PWM input). Each channel measures the duty cycle (fraction of time HIGH) during each incoming PWM cycle, and immediately presents *and holds* the corresponding correct output voltage. These particular devices are available in 8-, 10-, or 12-bit resolution versions, with internal 10 ppm/°C voltage reference and monotonic rail-to-rail voltage output. They are a great improvement over the classic technique of lowpass filtering a PWM input. The possibilities are mind-boggling!

<sup>&</sup>lt;sup>15</sup> You could instead use a differential amplifier between the two sense resistors, with a single ADC channel digitizing the resulting bipolarity signal.

<sup>&</sup>lt;sup>16</sup> In motor-drive applications it's often desirable to keep the drive frequency above audibility, so you don't drive people nuts. In this example we'd have to use a modulus *N*=800 or less, throwing out another bit of control resolution.

<sup>&</sup>lt;sup>17</sup> There are families of ICs, intended for speaker-driving audio power output stages, that accept a digital input stream in a standard audio format (such as I<sup>2</sup>S), and create as output a  $\Delta\Sigma$ -like switching waveform to drive a MOSFET H-bridge. Some of these include the MOSFETs on-chip – a single-chip PCM-to-speaker solution.

Figure 13.12. Controlling a torque motor with pulse-width modulation.

# 13.2.9 Frequency-to-voltage converters

In conversion applications the "digital" input may be a train of pulses or other waveform of some frequency; in that case, direct conversion to a voltage is sometimes more convenient than the alternative of counting for predetermined time, and then converting the binary count as in the preceding methods. In direct F/V conversion, a standard pulse is generated for each input cycle; it may be a voltage pulse or a pulse of current (i.e., a fixed amount of charge).

An RC lowpass filter or integrator then averages the pulse train, giving an output voltage proportional to the average input frequency. Of course, some output ripple results, and the lowpass filter necessary to keep this ripple less than the D/A precision (e.g.,  $\frac{1}{2}$ LSB) will, in general, cause a slow output response. To ensure less than  $\frac{1}{2}$ LSB output ripple, the time constant  $\tau$  of a simple *RC* lowpass filter must be at least  $\tau \ge 0.69(n+1)T_0$ , where  $T_0$  is the output period of the *n*-bit F/V converter corresponding to maximum input frequency. The output of this RC network will settle to  $\frac{1}{2}$  LSB, following a full scale change at the input, in 0.69(n+1) filter time constants. In other words, the output settling time to  $\frac{1}{2}$ LSB will be approximately  $t = 0.5 (n+1)^2 T_0$ . A 10-bit F/V converter with 100 kHz maximum input frequency, smoothed with an RC filter, will have an output-voltage settling time of 0.6 ms. With more complicated lowpass filters (sharp cutoff) you can get improved performance. Before you get carried away with fancy filter design, however, you should remember that F/V

techniques are most often used when a voltage output is not what's needed. For some perspective, see the previous discussion about intrinsically slow loads in connection with pulse-width modulation (§13.2.8).

# 13.2.10 Rate multiplier

This is a somewhat rarified method, of occasional (very occasional!) utility. A "rate multiplier" is a bit of clocked synchronous logic that accepts a multibit digital input quantity (binary or BCD), and that passes (or blocks) clock pulses to its single output line with an average rate proportional to that digital quantity. You can get these as standard logic (CD4089, CD4527, or SN7497), or you can make your own. Then simple averaging, as in the preceding F/V converter, can be used to generate a dc output proportional to the digital input code, although in this case the resulting output time constant may be intolerably long, because the rate-multiplier output will have to be averaged for a time equal to the longest output period it can generate (i.e.,  $2^n/f_{\text{clk}}$  for a rate multiplier with an *n*-bit rate-setting input). As with PWM, rate multipliers are most useful when the output is intrinsically averaged by the slowly responding characteristics of the load itself.

An application for which this is suited is in digital temperature control, where complete cycles of ac power are switched across the heater for each rate-multiplier output pulse. In this application the rate multiplier is arranged so that its lowest output frequency is an integral submultiple of 120 Hz, and a solid-state relay (or triac) is used to switch the ac power (at zero crossings of its waveform) from logic signals.

Note that the last four conversion techniques involve some time averaging, whereas the resistor-ladder and current-source methods are "instantaneous," a distinction that also exists in the various methods of analog-to-digital conversion. Whether a converter averages the input signal or converts an instantaneous sample of it can make an important difference, as we will see shortly in some examples.

# 13.2.11 Choosing a DAC

To guide you in choosing a DAC for a particular application, we've assembled in Tables 13.2 and 13.3 a representative selection of DACs of various precisions and speeds. This listing is by no means exhaustive, but it does include many of the more popular converters and some more recent entries that were intended as improved replacements.

When looking for a DAC for some application, here are some issues to keep in mind:

- 1. resolution;

- 2. speed (settling time, update rate);

- accuracy (linearity, monotonicity; external trimming required?);

- input structure (parallel or serial? latched? CMOS/TTL/ECL-compatible?);

- reference (internal, or externally supplied? if external, MDAC?);

- output structure (current output? compliance? voltage output? range?);

- 7. required supply voltages and power dissipation;

- 8. single or multiple DACs per package;

- 9. package style;

- 10. price.

# 13.3 Some DAC application examples

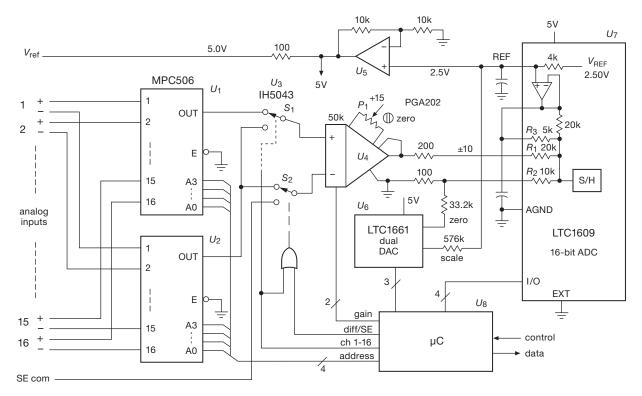

It's always helpful to get a guided tour of a real-world application example, to get a sense of the details wherein the devil resides. It's remarkably easy to put together a circuit that delivers nowhere near the performance that its converter is capable of. The four examples in this section illustrate some of the things you've got to worry about when using a DAC.

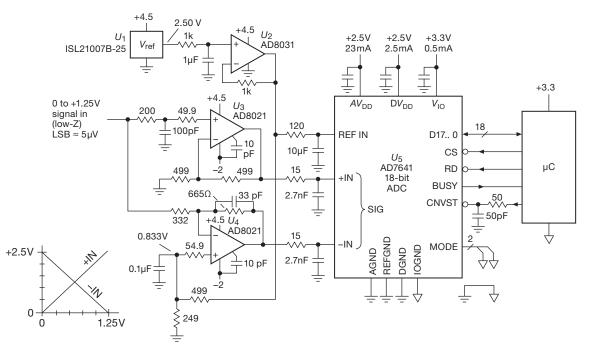

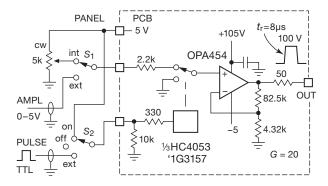

#### 13.3.1 General-purpose laboratory source

In our research laboratories it's common to control experimental parameters with low-noise analog voltages, which need to be highly stable over temperature and time. For example, electromagnetic traps for ions and molecules require precise voltages applied to pairs of electrostatic plates and precise currents through coils. Given the diversity of applications, the output range should be selectable in both polarity and span.

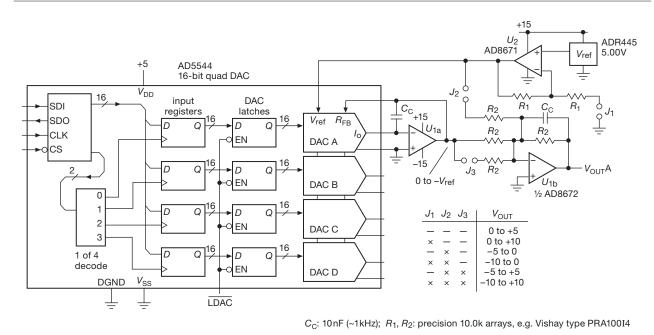

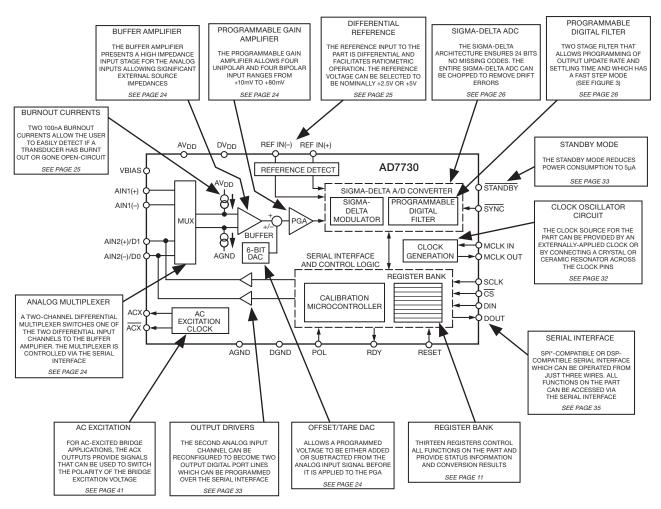

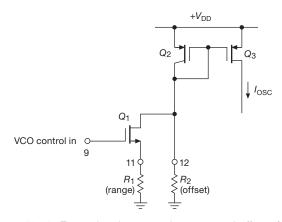

Figure 13.13 shows the business end of a popular product (the "BabyDAC"<sup>18</sup>) from our university's Electronic Instrument Design Laboratory. The core is the AD5544, a quad 16-channel current-output multiplying DAC that accepts an external reference voltage and outputs a set of four currents into an external node held at ground. You generate a voltage output with an external op-amp, using the matched internal feedback resistor. The internal structure for each channel is an R-2R ladder driven by  $V_{ref}$ , and a set of switches that connect each 2R leg either to the  $I_0$  output or to ground. The external reference voltage can be of either polarity, in the range  $\pm 10$  V. In fact, it can be a *signal* whose instantaneous voltage is multiplied by the digital input code to produce an output signal (hence a "multiplying DAC"); in such an application it has a signal bandwidth to audio frequencies and beyond.<sup>19</sup>

For this application the designer used a static  $V_{\text{ref}}$ , derived from the low-noise ADR440-series of voltage references (§9.10.3) based on a JFET analog of the standard BJT bandgap reference. The outboard circuitry is rigged up to provide jumper-selectable output-voltage ranges, both unipolarity and bipolarity; so  $J_1$  selects a reference voltage of +5 V or +10 V. Jumper  $J_3$  selects a gain of -2 for the output amplifier, doubling the span of  $U_{1a}$ 's output; and jumper  $J_2$  offsets the output by the selected value of  $V_{\text{ref}}$ . With these three jumpers you can select any of the six  $V_{\text{out}}$  ranges listed in the figure.

That's the basic circuit. With ideal components the output would be precise, noiseless, and drift-free. We live in a real world, though, in which we have to choose among available components to provide the best balance of necessary compromises. For the kind of laboratory applications we have in mind, stability and low noise are paramount. In the noise department the voltage reference is usually the biggest troublemaker, thus the choice of the

<sup>&</sup>lt;sup>18</sup> One of hundreds of elegant circuits and instruments from the everprolific Jim Macarthur, EIDL's design guru.

<sup>&</sup>lt;sup>19</sup> Caution, here: the datasheet lists a "reference multiplying bandwidth" of 2 MHz, but that's measured at full-scale digital code. The bandwidth is more like 20 kHz if you want 0 to -50 dB digital control. See §13.2.4.

Figure 13.13. General-purpose programmable laboratory source, designed with the four-channel DAC5544 for low noise and good stability. Use an isolator for the SPI digital link signals to minimize coupled digital noise.

"ultra-low-noise" ADR445, among the quietest with its  $\sim 2 \,\mu$ Vpp typical low-frequency (0.1–10 Hz) noise. Its drift spec is also quite good (1 ppm/°C typ, 3 ppm/°C max).<sup>20</sup> Reference noise can be reduced by *RC* filtering (see Figure 13.19 on page 898 for an example), or, if you're desperate, by paralleling the outputs of several references (with small ballasting resistors to ensure current sharing). The op-amps are quiet by comparison: 0.1  $\mu$ Vpp (max) low-frequency noise; similarly, the noise contributed by the DAC is negligible.

In this circuit the op-amp gains are rolled off around 1 kHz to minimize high-frequency noise at the output (originating in the reference, and in the DAC's code-change glitches). This bandwidth was chosen somewhat arbitrarily, on the assumption that the outputs are not going to be changing rapidly. The output bandwidth could be extended by a decade if the DAC were being programmed near its maximum rate. Or, for an application that is basically quasi-static, you could limit the bandwidth still further.

For the output *stability* it's common to look for specifications of drift with temperature and with time. The typical voltage tempcos here are 1 ppm/°C for the reference and for the DAC (thus the gain: the corresponding full-scale tempco is  $5 \mu V/^{\circ}C$  or  $10 \mu V/^{\circ}C$ ), and  $0.3 \mu V/^{\circ}C$  for the op-amps (which scales according to the gain jumper, either  $\times 1$  or  $\times 2$ ). With BJT-input op-amps you have to worry about input bias current and its tempco. For these op-amps the bias current is 3 nA (typ), with no tabulated tempco; however, there's an unsatisfying graph of  $I_{\rm B}$  versus temperature that suggests a tempco in the range of 5 pA/°C. With the circuit's 5k (or less) impedance seen at the op-amp inputs, this amounts to a 25 nV/°C drift, entirely negligible in comparison with everything else that's going on.

Manufacturers tend to be shy about specifying drift over *time*. For the components here there's no long-term drift spec for the DAC or op-amps. The ADR445 voltage reference specifies 50 ppm typical drift over 1000 hours, but with an interesting footnote that reads "The long-term stability specification is noncumulative. The drift in the subsequent 1000-hour period is significantly lower than in the first 1000-hour period."<sup>21</sup>

<sup>&</sup>lt;sup>20</sup> You'd get lower drift with the best-in-class MAX6350, at 1 ppm/°C max, but with somewhat greater noise: 3 µVpp.

<sup>&</sup>lt;sup>21</sup> Curiously, some manufacturers prefer to specify the long-term drift per *square root* of time, suggestive either of a decreasing drift as the part ages, or perhaps a random walk. An example is the astonishing LTZ1000 ovenized zener, with a specified long-term drift of  $2 \mu V / \sqrt{kHr}$  (typ), and a claimed typical tempco of 0.05 ppm/°C.

| Table 13 | 3.2 \$ | Selecte                     | ed D     | )-tc                | -A Co                   | nvert                 | ers <sup>a</sup>     |                            | ŧ                           |                        |             |       |                           |                           |               |            |             |               |    |             |              |          |             |           |          |

|----------|--------|-----------------------------|----------|---------------------|-------------------------|-----------------------|----------------------|----------------------------|-----------------------------|------------------------|-------------|-------|---------------------------|---------------------------|---------------|------------|-------------|---------------|----|-------------|--------------|----------|-------------|-----------|----------|

| Part #   | Bits   | settle <sup>t</sup><br>(µs) | Channels | Output <sup>b</sup> | Cost<br>qty25<br>(\$US) | Total S<br>min<br>(V) | Supply<br>max<br>(V) | Single supply <sup>c</sup> | )<br>(Wanger Supply Current | Interface <sup>d</sup> | Bipolar sig | Latch | Internal Ref <sup>e</sup> | External Ref <sup>g</sup> | Rail-rail out | Sleep Mode | Multiplying | 5V inputs OK? | Pa | cka<br>DIOS | ges<br>dOSLL | SOT-23 , | Smaller   5 | Monotonic | Comments |

| AD5300   | 8      | 6                           | 1        | V                   | 2.28                    | 2.7                   | 5.5                  | •                          | 0.14                        | S                      | -           | •     | -                         | $V_{S}$                   | •             | •          | -           | -             | -  | -           | 8            | 6        | -           | •         | A,J      |

| MCP4706  | 8      | 6                           | 1        | V                   | 0.60                    | 2.7                   | 5.5                  | ٠                          | 0.21                        | Ι                      | -           | •     | -                         | •                         | •             | •          | -           | -             | -  | -           | -            | 6        | 6           | •         | M,Z6     |

| AD8801   | 8      | 0.6                         | 8        | V                   | 6.20                    | 3                     | 5.5                  | ٠                          | 0.001                       | S                      | -           | •     | -                         | •                         | •             | •          | -           | -             | 16 | 16          | -            | -        | -           | •         | B,D      |

| DAC0808  | 8      | 0.15                        | 1        | Ι                   | 1.30                    | 7                     | 36                   | -                          | 2.6                         | Р                      | ٠           | -     | -                         | •                         | -             | -          | •           | •             | 16 | 16          | -            | -        | -           | •         | É        |

| DAC08    | 8      | 0.085                       | 1        | Ι                   | 1.61                    | 9                     | 36                   | -                          | 3.6                         | Р                      | ٠           | -     | -                         | •                         | -             | -          | •           | •             | 16 | 16          | -            | -        | -           | •         | E,F      |

| LTC1663  | 10     | 30                          | 1        | V                   | 3.70                    | 2.7                   | 5.5                  | ٠                          | 0.06                        | 2                      | -           | •     | 1.25                      | •                         | ٠             | •          | -           | -             | -  | 8           | -            | 5        | -           | ٠         | A,G      |

| LTC1669  | 10     | 30                          | 1        | V                   | 2.39                    | 2.7                   | 5.5                  | ٠                          | 0.06                        | Ι                      | -           | ٠     | 1.25                      | •                         | ٠             | ٠          | -           | •             | -  | 8           | -            | 5        | -           | ٠         | A,G      |

| AD5620   | 12     | 10                          | 1        | V                   | 3.81                    | 4.5                   | 5.5                  | ٠                          | 0.55                        | S                      | -           | ٠     | 2.5                       | -                         | ٠             | ٠          | -           | -             | -  | -           | -            | 8        | -           | ٠         | C,H      |

| DAC121   | 12     | 8                           | 1        | V                   | 2.07                    | 2.7                   | 5.5                  | ٠                          | 0.20                        | S                      | -           | ٠     | -                         | $V_{S}$                   | ٠             | ٠          | -           | -             | -  | -           | 8            | 6        | -           | ٠         | Á        |

| DAC7611  | 12     | 7                           | 1        | V                   | 6.05                    | 4.75                  | 5.25                 | ٠                          | 0.50                        | S                      | -           | ٠     | 4                         | -                         | -             | -          | -           | ٠             | 8  | 8           | -            | -        | -           | ٠         | K,L      |

| MCP4725  | 12     | 6                           | 1        | V                   | 0.80                    | 2.7                   | 5.5                  | ٠                          | 0.20                        | Ι                      | -           | ٠     | -                         | $V_{S}$                   | ٠             | ٠          | -           | -             | -  | -           | -            | 6        | -           | ٠         | M        |

| AD7845   | 12     | 5                           | 1        | V                   | 10.00                   | 28                    | 32                   | -                          | 4.6                         | Ρ                      | ٠           | ٠     | -                         | ٠                         | -             | -          | ٠           | ٠             | -  | -           | -            | -        | -           | ٠         | Ν        |

| MCP4921  | 12     | 4.5                         | 1,2      | V                   | 1.64                    | 2.7                   | 5.5                  | ٠                          | 0.20                        | S                      | -           | ٠     | -                         | ٠                         | ٠             | ٠          | ٠           | -             | 8  | 8           | 8            | -        | -           | ٠         | O,P      |

| TLV5638  | 12     | 1                           | 2        | V                   | 10.56                   | 2.7                   | 5.5                  | ٠                          | 4.3                         | S                      | -           | ٠     | 2                         | ٠                         | ٠             | ٠          | -           | ٠             | -  | 8           | 20           | -        | -           | ٠         | Q        |

| TLV5630  | 12     | 1                           | 8        | V                   | 14.87                   | 2.7                   | 5.5                  | ٠                          | 16                          | S                      | -           | ٠     | 2                         | ٠                         | ٠             | -          | -           | ٠             | -  | 20          | 20           | -        | -           | ٠         | A,G,Q,R  |

| DAC5672  | 14     | 0.020                       | 2        | Ι                   | 22.42                   | 3                     | .3 <sup>n</sup>      | ٠                          | 100                         | Ρ                      | -           | ٠     | 1.2                       | ٠                         | -             | ٠          | -           | -             | -  | -           | 48           | -        | -           | -         | S        |

| AD9739   | 14     | 0.013                       | 1        | Ι                   | 56.00                   | 1.8 ar                | าd 3.3 <sup>n</sup>  | -                          | 400,70                      | L                      | -           | ٠     | 1.2                       | ٠                         | -             | ٠          | -           | -             | -  | -           | -            | -        | 160         | -         | Т        |

| AD5660   | 16     | 10                          | 1        | V                   | 5.90                    | 4.5                   | 5.5                  | ٠                          | 0.6                         | S                      | -           | ٠     | 2.5                       | -                         | ٠             | ٠          | -           | -             | -  | -           | -            | 8        | -           | ٠         | C,U      |

| DAC8564  | 16     | 10                          | 4        | V                   | 11.91                   | 2.7                   | 5.5                  | ٠                          | 1.0                         | S                      | -           | ٠     | 2.5                       | ٠                         | ٠             | ٠          | -           | -             | -  | -           | 16           | -        | -           | ٠         | A,V      |

| LTC2656  | 16     | 8.9                         | 8        | V                   | 29.50                   | 2.7                   | 5.5                  | ٠                          | 3.0                         | S                      | -           | ٠     | 2.5                       | ٠                         | ٠             | ٠          | -           | ٠             | -  | -           | 20           | -        | 20          | ٠         | C,W      |

| AD5686R  | 16     | 5                           | 4        | V                   | 9.90                    | 2.7                   | 5.5                  | ٠                          | 1.1                         | S                      | -           | ٠     | 2.5                       | 0                         | ٠             | ٠          | -           | ٠             | -  | -           | 16           | -        | 16          | ٠         | C,X      |

| AD5541A  | 16     | 1                           | 1        | V                   | 15.39                   | 2.7                   | 5.5                  | ٠                          | 0.13                        | S                      | -           | ٠     | -                         | ٠                         | ٠             | -          | •           | ٠             | -  | -           | 10           | -        | 8           | ٠         | A,Y      |

| LTC1668  | 16     | 0.020                       | 1        | Ι                   | 18.81                   |                       | nd -5 <sup>n</sup>   | -                          | 3.33                        | Ρ                      | ٠           | ٠     | 2.5                       | ٠                         | -             | -          | -           | ٠             | -  | -           | 28           | -        | -           | -         | Z        |

| DAC5682  | 16     | 0.010                       | 2        | Ι                   | 45.14                   | 1.8 ar                | nd 3.3 <sup>n</sup>  | -                          | 500,133                     | L                      | -           | ٠     | 1.2                       | ٠                         | -             | ٠          | -           | -             | -  | -           | -            | -        | 64          | -         | Z2       |

| AD5780   | 18     | 2.5                         | 1        | V                   | 32.23                   | 5                     | 33                   | -                          | 10,10                       | S                      | ٠           | ٠     | -                         | ٠                         | -             | ٠          | -           | ٠             | -  | -           | -            | -        | 24          | ٠         | A,Z3     |

| DAC9881  | 18     | 5                           | 1        | V                   | 28.98                   | 2.7                   | 5.5                  | ٠                          | 0.85                        | S                      | -           | ٠     | -                         | ٠                         | ٠             | ٠          | -           | -             | -  | -           | -            | -        | 24          | ٠         | C,Z4     |

| AD5791   | 20     | 1                           | 1        | V                   | 53.53                   | 10                    | 33                   | -                          | 4.2                         | S                      | ٠           | ٠     | -                         | •                         | -             | -          | -           | -             | -  | -           | 20           | -        | -           | ٠         | Z5       |

Notes: (a) see also MDAC Table 13.3; listed by increasing resolution, then speed. (b) V-voltage; I-current. (c) operates from a single positive supply. (d) 2 - 2-wire serial; I - I<sup>2</sup>C; L - parallel LVDS; P - parallel; S - SPI. (e) 2 = 2.048; 4 = 4.096. (g) can use ext ref. (n) nominal. (o) non-R version. (t) typical. Comments: A: power-on to 0V. B: power-on to midscale. C: power-on to 0V or midscale. D: TrimDAC, pot replacement, Z<sub>out</sub>=5kΩ. E: multiplying, to ~1MHz. F: compliance to -10V and +18V. G: double buffered for simultaneous updating. H: 14-bit=AD5640, 16-bit=AD5660; 0.2%, 5ppm/°C ref. J: digital gain & offset adjustment. K: DAC8512 2nd source. L: power-on to 0V plus a CLR pin. M: power-on state from on-chip EEPROM. N: multiplying, to 600kHz. O: multiplying, to 450kHz; 14-pin dual=4922. P: power-on to hi-Z. Q: programmable settling time. R: 10-bit=TLV5631; 8-bit=TLV5632. S: 275Msps; 1.5ns to 90%; DAC2904, AD9767 2nd source. T: RF synthesis, 2.5Gsps. U: ext ref version = 5662; 0.2%, 5ppm/°C ref. V: 14-bit=DAC8164; 12-bit=DAC7564; low glitch; 0.004%, 2ppm/°C ref. W: 0.2%, 2ppm/°C ref; also 4.096 Vref and 12-bit versions. X: 2ppm/°C ref. Y: multiplying, to ~1MHz; low glitch; 0.1ppm/°C; 12nV//Hz; unbuffered output. Z: low glitch; 50Msps; 12-bit and 14-bit versions. Z2: 1Gsps; FIFO; clock PLL; on-chip digital filters. Z3: 8nV//Hz; 0.02ppm/°C; 3 pwr supplies; "system ready." Z4: 0.3ppm/°C; 24nV//Hz. Z5: 0.05ppm/°C; 7.5nV/rtHz. **Z6:** 10-bit=MCP4716; 12-bit=MCP4726.

As we remarked at the outset, for the intended application it is noise and drift that are most important. By contrast, the absolute accuracy is not particularly impressive: the worst-case specs are  $\pm 200$  ppm for the voltage reference,  $\pm 75 \,\mu\text{V}$  for the op-amps, and  $\pm 3 \,\text{mV}$  full-scale gain error for the DAC. Translated to units of 16-bit LSB steps, and taking the output range to be  $\pm 10$  V (for which an LSB is 0.3 mV), these correspond to  $\pm 13$  LSB,  $\pm 0.5$  LSB, and  $\pm 10$  LSB.

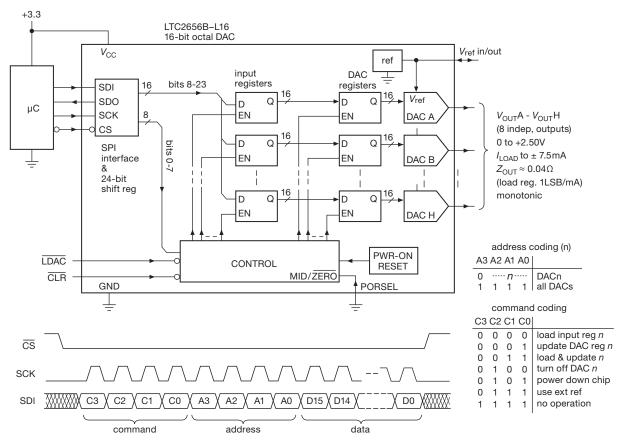

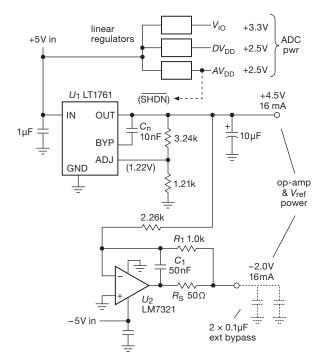

#### 13.3.2 Eight-channel source

If your application does not need the flexibility of output polarities and scale factors of the last example, and if you can tolerate a bit more noise and drift, you can do pretty well with a fully integrated multiple-section voltageoutput DAC, for example the LTC2656 in Figure 13.14. This particular IC includes an internal voltage reference of good stability ( $\pm 2 \text{ ppm/}^{\circ}\text{C}$  typ,  $\pm 10 \text{ ppm/}^{\circ}\text{C}$  max), with a 1 ppm/°C typical full-scale tempco for the DAC

| Table 13   |      |                        |          | Type   | st                   | P          | ower       | Suppl | ies                 | Range   | t Range | <b>/</b> supply  | ce <sup>c</sup>        | Distortion (1kHz) |                      | (nV//Hz at 1kHz) | Bandwidth      |     | Feedthrough <sup>b</sup> | Pack | kage | es, P |         | ents     |

|------------|------|------------------------|----------|--------|----------------------|------------|------------|-------|---------------------|---------|---------|------------------|------------------------|-------------------|----------------------|------------------|----------------|-----|--------------------------|------|------|-------|---------|----------|

| Part #     | Bits | tsettle<br>typ<br>(μs) | Channels | Output | o<br>qty25<br>(\$US) | min<br>(V) | max<br>(V) |       | ative<br>max<br>(V) | (<) (∧) | (S Vout | typ<br>(µA)      | Interface <sup>c</sup> |                   | @ <b>V</b> pp<br>(V) | Noise            | typ @<br>(MHz) |     | (MHz)                    | DIP  | SOIC | TTSOP | Smaller | Comments |

| AD8842     | 8    | 2.9                    | 8        | V      | 13.71                | 4.75       | 5.25       | . ,   | 5.25                | . ,     | ±3      | 10               | S                      | -80               | 4                    | 78               | 1.5            | 0.1 | 0.25                     |      | 24   |       |         | A        |

| TLC7528    | 8    | 0.1                    | 2        | Ι      | 3.47                 | 4.75       | 15         | -     | -                   | ±25     | ±25     | 2000             | Ρ                      | -85               | 6                    | -                | -              | -   | -                        | 20   | 20   | 20    | -       | В        |

| MCP4921    | 12   | 4.5                    | 1        | V      | 1.64                 | 2.7        | 5.5        | -     | -                   | 0 to Vs | 0 to Vs | 200              | S                      | -73               | 0.4                  | -                | 0.45           | 0.4 | -                        | 8    | 8    | 8     | -       | С        |

| AD/LTC7541 | 12   | 0.6                    | 1        | Ι      | 6.00                 | 5          | 16         | -     | -                   | ±10     | ±0.5    | 100              | Ρ                      | -                 | -                    | -                | -              | -   | -                        | 18   | 18   | -     | 20      | D        |

| AD7943,5,8 | 12   | 0.6                    | 1        | Т      | 7.78                 | 3          | 5.5        | -     | -                   | ±10     | ±0.3    | 0.005            | S,P                    | -83               | 17                   | 35               | -              | -   | 2                        | 16   | 20   | 20    | -       | Е        |

| LTC8043    | 12   | 0.25                   | 1        | Ι      | 8.10                 | 4.75       | 5.25       | -     | -                   | ±10     | ±0.5    | 100 <sup>m</sup> | S                      | -108              | 17                   | 17 <sup>r</sup>  | n _            | -   | 1                        | 8    | 8    | 8     | -       | F        |

| AD5443     | 12   | 0.06                   | 1        | Ι      | 4.87                 | 3          | 5.5        | -     | -                   | ±10     | ±0.3    | 0.6 <sup>m</sup> | S                      | -81               | 3.5                  | 25               | 10             | 7   | 10 <sup>e</sup>          | -    | -    | 10    | -       | G        |

| DAC7821    | 12   | 0.05                   | 1        | Ι      | 6.38                 | 2.5        | 5.5        | -     | -                   | ±15     | ±0.3    | 0.8              | Ρ                      | -105              | -                    | 18               | 10             | 7   | 0.8                      | -    | -    | 20    | -       | Н        |

| AD5544     | 16   | 0.9                    | 4        | Ι      | 27.43                | 2.7        | 5.5        | 0     | 5.5                 | ±15     | ±0.3    | 5 <sup>m</sup>   | S                      | -98               | 5                    | 7                | 5              | 5   | -                        | -    | -    | 28    | 32      | I,J      |

| DAC8814    | 16   | 0.5                    | 4        | Ι      | 29.06                | 2.7        | 5.5        | -     | -                   | ±15     | ±0.3    | 2                | S                      | -105              | 5                    | 12               | 10             | 0.3 | 2                        | -    | -    | 28    | -       | J        |

| DAC8820    | 16   | 0.5                    | 1        | Ι      | 16.98                | 2.7        | 5.5        | -     | -                   | ±15     | ±0.3    | 5 <sup>m</sup>   | Ρ                      | -105              | 17                   | 10               | 8              | 5   | 0.15                     | -    | -    | 28    | -       | Κ        |

| LTC2757    | 18   | 2.1                    | 1        | I      | 57.43                | 2.7        | 5.5        | -     | -                   | ±15     | ±0.3    | 0.5              | Ρ                      | -110              | 5                    | 13               | -              | -   | 1 <sup>e</sup>           | -    | -    | -     | 48      | L        |

Notes: (a) listed by increasing accuracy and speed; all are monotonic, and all have latches except AD/LTC7541; see also DAC Table 13.2. (b) capacitive coupling causes a 6dB/octave rising output (from the desired digital value of attenuation) at high frequencies; the listed value is the frequency at which there is a +3dB increase relative to a -40dB programmed attenuation (i.e., an actual attenuation of -37dB). (c) 2 - 2-wire serial; I -1<sup>2</sup>C; P - parallel; S - SPI; L - parallel LVDS. (d) 65dB feedthrough at 100kHz. (e) 3dB loss, rather than feedthrough. (m) min or max. (n) nominal. (t) typical.

Comments: A: current conveyor,  $V_{out}=V_{in} \times (D/128 - 1)$ . B: 2nd source for AD7528. C: MCP4922=dual. D: 80dB feedthru @ 10kHz and full-swing. E: improved AD7543, -45, and -48; AD7545 & -48 are parallel interface. F: also DAC8043. G: 10-bit=AD5432, 8-bit=AD5426. H: parallel readback. I: 14-bit=AD5554. J: reset to zero or midscale. K: reset to zero. L: double buffer, readback, reset to zero.

outputs. The DAC's low-frequency (0.1-10 Hz) output noise is 8  $\mu$ Vpp, typical. This is four times the noise voltage of the previous example; taking into account the more limited output span (0–2.5 V), it represents a larger relative noise contribution still. The good news is the relative simplicity of this part: no external reference or amplifiers, and operation from a single positive supply.

The SPI digital interface is simple and clean: every transfer is 24 bits, with 4 bits to specify the channel number (with an option to load all channels with the same value), 4 bits to specify the operation, and 16 bits to carry the digital value. Each channel is double buffered, so you can load the next value into each channel's input buffer, then transfer them simultaneously to the DAC's register so that all outputs change to their new values at the same time.

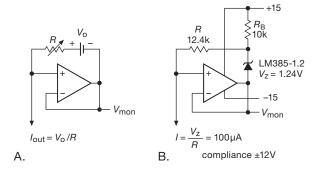

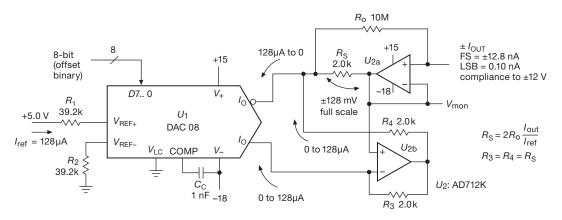

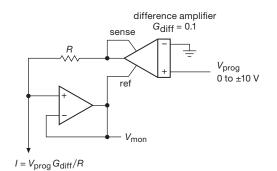

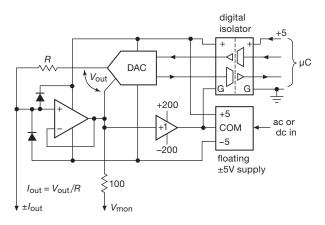

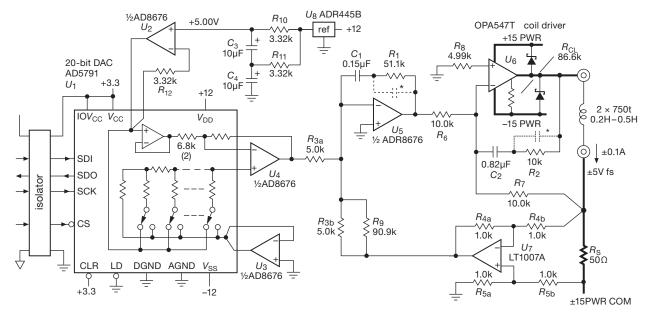

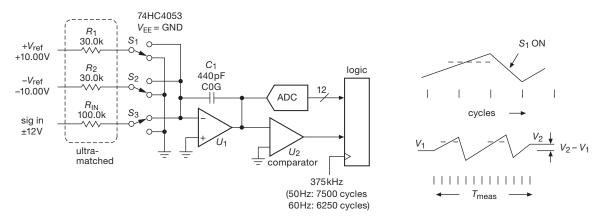

# 13.3.3 Nanoamp wide-compliance bipolarity current source